Specification

# **CPB907** Mezzanine CPU Module COM Express® mini, Type 10

# **User Manual**

Rev. 1.0 June 2015

The product described in this manual is compliant with all related CE standards.

Product Title: CPB907 Document name: CPB907 User Manual Manual version: 0.1 Copyright © 2015 Fastwel Co. Ltd. All rights reserved.

#### **Revision Record**

| Revision No. | Brief description of changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Board index | Revision date  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|

| 0.1          | Initial version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CPB907      | March 2013     |

| 1.00         | Item version: 1.2<br>Sections1.2 "General information", 1.5<br>"Board block diagram ", 1.7 "Module<br>versions" – there were changes related to<br>the RAM volume for various module versions<br>(DDR2 RAM volume for CPB907-03 version<br>has been increased up to 1 GB).<br>Section 1.4 "Module power supply" –<br>changes regarding requirements to power<br>supply parameters.<br>Section 1.8 "Delivery checklist" has been<br>added with information on cooling system<br>options.<br>Section 1.9 "Additional accessories" – order<br>number for development kit has been<br>changed (KIB1283-02).<br>Section 2.1 "General technical specifications<br>for CPB907" – changes related consumption<br>current of various versions of CPB907 were<br>made, added information on weight and<br>dimensions of the module with the installed<br>cooling system. | CPB907      | September 2013 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |                |

### **Contact Information**

|          | Fastwel Co. Ltd                                                | Fastwel Corporation US                                    |

|----------|----------------------------------------------------------------|-----------------------------------------------------------|

| Address: | 108 Profsoyuznaya st.,<br>Moscow 117437,<br>Russian Federation | 55 Washington St. #310<br>Brooklyn, New York 11201<br>USA |

| Tel.:    | +7 (495) 232-1681                                              | +1 (718) 554-3686                                         |

| Fax:     | +7 (495) 232-1654                                              | +1 (718) 797-0600                                         |

| E-mail:  | info@fastwel.com                                               | sales@fastwel.com                                         |

| Web:     | http://www.fastwel.com/                                        | http://www.fastwel.com/                                   |

# TABLE OF CONTENTS

| TRADEMARKS                                                         | 7  |

|--------------------------------------------------------------------|----|

| OWNERSHIP RIGHTS                                                   | 7  |

| COPYRIGHT                                                          | 7  |

| TRANSPORTATION, UNPACKING AND STORAGE                              | 8  |

| Transportation                                                     | 8  |

| Unpacking                                                          | 8  |

| Storage                                                            | 8  |

| MANUFACTURER'S WARRANTY                                            | 9  |

| Warranty Liability                                                 | 9  |

| Liability Limitation Right                                         | 9  |

| Warranty Period                                                    | 9  |

| Limitation of warranty liabilities                                 | 9  |

| Returning a product for repair                                     | 9  |

| Notation Conventions                                               | 10 |

| Safety precautions                                                 | 11 |

| SECTION 1: DESCRIPTION AND OPERATION OF CPB907                     |    |

| 1. Description and operation of CPB907                             | 12 |

| 1.1. Purpose                                                       | 12 |

| 1.2. General Information                                           | 12 |

| 1.3. Dimensions                                                    | 16 |

| 1.4. Module power supply                                           | 18 |

| 1.5. Block diagram of CPB907                                       | 18 |

| 1.6. Location of main components of CPB907                         | 19 |

| 1.7. Installation of CPB907 onto the carrier-board, cooling system |    |

| 1.8. Versions                                                      | 21 |

| 1.9. Delivery checklist                                            | 22 |

| 1.10. Additional accessories                                       | 22 |

| 1.11. Component parts of CPB907                                    | 23 |

| SECTION 2: TECHNICAL CHARACTERISTICS                               |    |

| 2.1. Technical specification                                       | 31 |

| 2.2. Allocation of hardware interrupts                             | 34 |

| 2.3. Module's DMA channels                                         | 34 |

| 2.4. Address I/O space                                             | 35 |

| 2.5. Address memory space                                          | 36 |

| 2.6. Use of GPIO ports                                             | 36 |

| 2.7 Tables of module connectors contacts                           | 38 |

| SECTION 3: INTENDED USE OF CPB907                                  |    |

| 3. Intended use of CPB907                                          | 51 |

| 3.1. Installation of module switches                               | 51 |

| 3.2. Basic Input-output system (BIOS)                              | 52 |

| Main                                                               | 53 |

| Advanced (additional settings)                                     | 54 |

| PCI Subsystem Settings                                             | 55 |

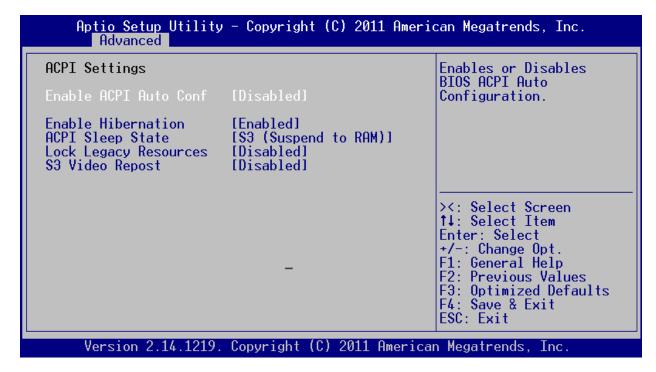

| ACPI Settings                                                      |    |

| CPU Configuration                                                  | 57 |

| Hardware Monitoring                | 58 |

|------------------------------------|----|

| USB Configuration                  | 59 |

| Thermal Configuration              | 60 |

| SDIO Configuration                 | 61 |

| SMSC Super IO Configuration        | 62 |

| Serial Port Console Redirection    | 63 |

| Chipset (additional settings)      | 64 |

| North Bridge Chipset Configuration | 65 |

| South Bridge Chipset Configuration | 66 |

| IOH Configuration                  | 67 |

| Boot                               | 68 |

| Security                           | 69 |

| Save & Exit                        | 70 |

| 3.3. Basic software                | 71 |

| 3.4. Service programs              | 71 |

| ANNEX A                            | 73 |

# List of tables

| Table 1-1: Requirements for power supply parameters                        |    |

|----------------------------------------------------------------------------|----|

| Table 1-2: Options of CPB907 Module (differences of the supplied versions) | 21 |

| Table 1-3: Additional accessories for CPB907 CPU Module                    |    |

| Table 1-4: Values of frequency dividers for serial ports                   | 27 |

| Table 1-5: Purpose of CPB907 LEDs                                          | 29 |

| Table 2-1: Requirements for electric power supply of CPB907                | 31 |

| Table 2-2: Characteristics of GPIO                                         | 31 |

| Table 2-3: Characteristics of serial ports                                 | 31 |

| Table 2-4: Characteristics of SATA port                                    | 32 |

| Table 2-5: Characteristics of USB, Ethernet ports                          | 32 |

| Table 2-6: Mechanical characteristics                                      |    |

| Table 2-7: Environmental conditions                                        |    |

| Table 2-8: Addresses of hardware interrupts                                |    |

| Table 2-9: Module's DMA channels                                           | 34 |

| Table 2-10: Allocation of address I/O space                                | 35 |

| Table 2-11: Memory device address                                          | 36 |

| Table 2-12: Purpose of GPIO ports of E6x0T processor                       |    |

| Table 2-13: Purpose of GPIO ports of EG20T chipset                         |    |

| Table 2-14: Purpose of contacts of COM Express connector (XS1)             |    |

| Table 3-1: Purpose of switches for module configuration                    |    |

| Table 3-2: Description of "Main" menu                                      |    |

| Table 3-3: Description of "Advanced" menu                                  | 54 |

| Table 3-4: Description of "PCI Subsystem Settings" menu                    |    |

| Table 3-5: Description of "ACPI Settings" screen                           | 56 |

| Table 3-6: Description of "CPU Configuration" screen                       |    |

| Table 3-7: Description of "USB Configuration" screen                       |    |

| Table 3-8: Description of "Thermal Configuration" screen                   | 60 |

| Table 3-9: Description of "SDIO Configuration" menu                        |    |

| Table 3-10: Description of "SMSC Super IO Configuration" menu              |    |

| Table 3-11: Description of "Chipset" menu                                  |    |

| Table 3-12: Description of "North Bridge Chipset Configuration" menu       |    |

| Table 3-13: Description of "South Bridge Chipset Configuration" menu       |    |

| Table 3-14: Description of "IOH Configuration" menu (additional settings)  | 67 |

| Table 3-15: Description of "Boot" menu                                     | 68 |

| Table 3-16: Description of "Security" menu                                 | 69 |

| Table 3-17: Description of "Save & Exit" menu                              | 70 |

| Annex A. Terms and abbreviations                                           | 73 |

#### List of figures

| Fig. 1-1: Overall and fitting dimensions of CPB907 (bottom and side view)                       |                   |

|-------------------------------------------------------------------------------------------------|-------------------|

| Fig. 1-2: Overall dimensions of the carrier-board's installation spot)                          |                   |

| Fig. 1-3: Block diagram of CPB907                                                               | 18                |

| Fig. 1-4: Location of main components of CPB907                                                 | 19                |

| Fig. 1-5: Installation of CPB907 onto the carrier-board                                         |                   |

| Fig. 1-6: Dimensions of the heat-dissipation plate                                              | 20                |

| Fig. 1-7: Overall Dimensions of heat-sink (ACS30067) and dependency of its heat-transfer on the | e generated power |

| and air-flow rate                                                                               |                   |

| Fig. 1-8: Main 220-pin high-density connector of CPB907 module (viewed from the bottom of CPB   | 3907)23           |

| Fig. 1-9: Connection of the COM-Express CPB907 and counterpart of the carrier-board             | 23                |

| Fig. 3-1: Screen during module booting (POST)                                                   | 52                |

| Fig. 3-2: Screen of "Main" menu                                                                 | 53                |

| Fig. 3-3: Screen of "Advanced" menu                                                             | 54                |

| Fig. 3-4: Screen of "PCI Subsystem Settings" menu                                               | 55                |

| Fig. 3-5: Screen of "ACPI Settings" menu                                                        |                   |

| Fig. 3-6: Screen of "CPU Configuration" menu                                                    | 57                |

| Fig. 3-7: Screen of "Hardware Monitoring" menu                                                  |                   |

| Fig. 3-8: Screen of "USB Configuration" menu                                                    | 59                |

| Fig. 3-9: Screen of "Thermal Configuration" menu                                                | 60                |

| Fig. 3-10: Screen of "SDIO Configuration" menu                                                  | 61                |

| Fig. 3-11: Screen of "SMSC Super IO Configuration" menu                                         |                   |

| Fig. 3-12: Screen of "Serial Port Console Redirection" menu                                     | 63                |

| Fig. 3-13: Screen of "Chipset" menu                                                             | 64                |

| Fig. 3-14: Screen of "North Bridge Chipset Configuration" menu                                  | 65                |

| Fig. 3-15: Screen of "South Bridge Chipset Configuration" menu                                  |                   |

| Fig. 3-16: Screen of "IOH Configuration" menu                                                   |                   |

| Fig. 3-17: Screen of "Boot" menu                                                                | 68                |

| Fig. 3-18: Screen of "Security" menu                                                            | 69                |

| Fig. 3-19: Screen of "Save & Exit" menu                                                         | 70                |

All information in this document is provided for reference only, with no warranty of its suitability for any specific purpose. This information has been thoroughly checked and is believed to be entirely reliable and consistent with the product that it describes. However, Fastwel accepts no responsibility for inaccuracies, omissions or their consequences, as well as liability arising from the use or application of any product or example described in this document.

Fastwel Co. Ltd. reserves the right to change, modify, and improve this document or the products described in it, at Fastwel's discretion without further notice. Software described in this document is provided on an "as is" basis without warranty. Fastwel assumes no liability for consequential or incidental damages originated by the use of this software.

This document contains information, which is property of Fastwel Co. Ltd. It is not allowed to reproduce it or transmit by any means, to translate the document or to convert it to any electronic form in full or in parts without antecedent written approval of Fastwel Co. Ltd. or one of its officially authorized agents.

Fastwel and Fastwel logo are trademarks owned by Fastwel Co. Ltd., Moscow, Russian Federation. Ethernet is a registered trademark of Xerox Corporation. IEEE is a registered trademark of the Institute of Electrical and Electronics Engineers Inc. Intel is a trademark of Intel Corporation. Pentium M and Celeron M are trademarks of Intel Corporation. Microsoft is a trademark of the Microsoft corporation. In addition, this document may include names, company logos and trademarks, which are registered trademarks and, therefore, are property of their respective owners. Fastwel welcomes suggestions, remarks and proposals regarding the form and the content of this Manual.

# **Trademarks**

"Fastwel" logotype is a trademark belonging to Fastwel Group Co. Ltd., Moscow, Russian Federation.

Besides, this document may contain names, corporate logotypes and trademarks being registered trademarks; consequently, property rights to them belong to their respective legitimate owners.

# **Ownership Rights**

This document contains information being the property of Fastwel Group Co. Ltd. It can neither be copied nor transferred with the utilization of known media nor be stored in data storage and search systems without the prior written authorization of Fastwel Group Co. Ltd. To our best knowledge, the data in this document does not contain errors. However, Fastwel Group Co. Ltd cannot take responsibility for any inaccuracies and their consequences, as well as responsibility arising as a result of utilization or application of any diagram, product or example cited in this document. Fastwel Group Co. Ltd reserves the right to alter and update both this document and the product presented therein at its own discretion without additional notification.

# Copyright

This document cannot be copied, reproduced, transferred or converted to any electronic or machine-readable form without prior written permission of Fastwel Co. Ltd

# TRANSPORTATION, UNPACKING AND STORAGE

#### Transportation

The device should be transported in original manufacturer's separate packaging (transport packaging), which contains an individual antistatic bag and a cardboard box, in the closed transport (automobile, railway, air transportation in heated and pressurized compartments) in storage conditions 5 defined in the IEC 721-2-1 standard (GOST standard 15150-69) or in storage conditions 3 during sea transportation.

The packaged modules should be transported in accordance with the shipping rules, specified for this particular type of transport.

During handling and transportation operations, the packaged modules should not undergo sharp pounding, falls, shocks and exposure to atmospheric precipitation. The goods should be stored in a carrier vehicle in such a manner which will prevent their moving.

#### Unpacking

Prior to unpacking, after transportation at subzero temperature of ambient air the module(s) should be kept within 6 hours under storage conditions 1 defined in the IEC 721-2-1 standard (GOST standard 15150-69).

It is prohibited to place the packaged module close to the heat source, prior to unpacking.

Retain all original packaging at least until the warranty period is over. You may need it for shipments or for storage of the product.

After unpacking the product, you should inspect it for visible damage that could have occurred during shipping or unpacking. If damage is observed (usually in the form of bent component leads or loose socketed components), contact Fastwel's official distributor from which you have purchased the product for additional instructions.

### Storage

Module storage conditions for group 1 are defined in the IEC 721-2-1 standard (GOST standard 15150-69).

# MANUFACTURER'S WARRANTY

### **Warranty Liabilities**

The Manufacturer hereby guarantees the product conformity with the requirements of the 4013-025-72782511-09 technical conditions provided that the Consumer complies with the operating, storage, transportation and installation conditions and procedures, specified by the accompanying documents.

The Manufacturer hereby guarantees that the products supplied thereby are free from defects in workmanship and materials, provided operation and maintenance norms were observed during the currently established warranty period. The Manufacturer's obligation under this warranty is to repair or replace free of charge any defective electronic component being a part of a returned product.

Products that broke down through the Manufacturer's fault during the warranty period will be repaired free of charge. Otherwise the Consumer will be invoiced as per the current labor remuneration rates and expendable materials cost

# **Liability Limitation Right**

The Manufacturer shall not be liable for the damage inflicted to the Consumer's property because of the product breakdown in the process of its utilization.

# Warranty Period

The warranty period for the products made by Fastwel Group is 24 months since the sale date (unless otherwise provided by the supply contract).

The warranty period for the custom-made products is 36 months since the sale date (unless otherwise provided by the supply contract.

# Limitation of warranty liabilities

The above warranty liabilities shall not be applied:

To the products (including software), which were repaired or were amended by the employees, that do not represent the manufacturer. Exceptions are the cases where the customer has made repairs or made amendments to the devices in the strict compliance with instructions, preliminary agreed and approved by the manufacturer in writing;

To the products, broken down due to unacceptable polarity reversal (to the opposite sign) of the power supply, improper operation, transportation, storage, installation, mounting or accident.

# Returning a product for repair

1. Apply to Fastwel company or to any of the Fastwel's official representatives for the Product Return Authorization.

2. Attach a failure inspection report with a product to be returned in the form, accepted by the Manufacturer, with a description of the failure circumstances and symptoms.

3. Place the product in the consumer packaging (antistatic bag) and cardboard box, in which the product had been supplied. Failure to package in antistatic material will VOID all warranties of the Customer on a unilateral basis.

4. The customer pays for shipping the product to Fastwel or to an official Fastwel representative or dealer

# Notation Conventions

The CE marking is manufacturer's declaration that this product conforms to the requirements of the applicable EC directives.

#### **Caution: Electric Shock!**

This symbol warns about danger of electrical shock (> 60 V) when touching products or parts of them. Failure to observe the indicated precautions and directions may expose your life to danger and may lead to damage to your product. Please also see the below section, dedicated to regulations on operation with high voltage devices.

#### Warning, ESD Sensitive Device!

This symbol draws your attention to the information related to electro static sensitivity of your product and its components. To keep product safety and operability it is necessary to handle it with care and follow the ESD safety directions. Please also see the below section, dedicated to directions concerning handling the board and unpacking.

This sign marks warnings about hot surfaces. The surface of the heatsink and some components can get very hot during operation. Take due care when handling, avoid touching hot surfaces!

Information marked by this symbol is essential for human and equipment safety. Read this information attentively, be watchful..

#### This symbol and title marks important information to be read attentively for your own benefit.

# **General Safety Precautions**

This product was developed for fault-free operation. Its design provides conformance to all related safety requirements. However, the life of this product can be seriously shortened by improper handling and incorrect operation. That is why it is necessary to follow general safety and operational instructions below.

#### Regulations on safe handling of high voltage

All operations on this device must be carried out by sufficiently skilled personnel only.

#### Caution, Electric Shock!

Before installing this product into a system and before installing other devices on it, always ensure that switched off. This also refers to the installation of mezzanine boards.

Always disconnect external power supply cables during all handling and maintenance operations with the serious danger of electrical shock. This also refers to other lead wires.

#### **Unpacking, Inspection and Handling**

Please read the manual carefully before unpacking the module or mounting the device into your syster following:

#### **ESD Sensitive Device!**

Electronic modules and their components are sensitive to static electricity. Even a non-perceptible by H discharge can be sufficient to destroy or degrade a component's operation! Therefore, all handling ope this product must be performed with due care, in order to keep product integrity and operability: n Preferably, unpack or pack this product only at EOS/ESD safe workplaces. Otherwise, it is important to be electrically discharged before touching the product. This can be done by touching a metal part of your system case with your hand or tool. It is particularly important to observe anti-static precautions when setting jumpers or replacing components.

n If the product contains batteries for RTC or memory back-up, ensure that the module is not placed on conductive surfaces, including anti-static mats or sponges. This can cause shortcircuit and result in damage to the battery and other components.

n Store this product in its protective packaging while it is not used for operational purposes. **Unpacking**

The product is carefully packed in an antistatic bag and in a carton box to protect it against possible damage and harmful influence during shipping. Unpack the product indoors only at a temperature not less than +15°C and relative humidity not more than 70%. Please note, that if the product was exposed to the temperatures below 0°C for a long time, it is necessary to keep it at normal conditions for at least 24 hours before unpacking. Do not keep the product close to a heat source.

Following ESD precautions, carefully take the product out of the shipping carton box. Proper handling of the product is critical to ensure correct operation and long-term reliability. When unpacking the product, and whenever handling it thereafter, be sure to hold the module preferably

Specification

by the front panel, card edges or ejector handles. Avoid touching the components and connectors. Retain all original packaging at least until the warranty period is over. You may need it for shipments or for storage of the product.

#### Initial Inspection

Although the product is carefully packaged, it is still possible that shipping damages may occur. Careful inspection of the shipping carton can reveal evidence of damage or rough handling. Should you notice that the package is damaged, please notify the shipping service and the manufacturer as soon as possible. Retain the damaged packing material for inspection.

After unpacking the product, you should inspect it for visible damage that could have occurred during shipping or unpacking. If damage is observed (usually in the form of bent component leads or loose socketed components), contact Fastwel's official distributor from which you have purchased the product for additional instructions. Depending on the severity of the damage, the product may even need to be returned to the factory for repair. DO NOT apply power to the product if it has visible damage. Doing so may cause further, possibly irreparable damage, as well as result in a fire or electric shock hazard.

If the product contains socketed components, they should be inspected to make sure they are seated t

# Section 1 1. Description and operation of CPB907 1.1. Purpose

CPB907 CPU Module, implemented in the standard COM Express® mini format, provides developers of high-reliable small scale systems with such functions as compatibility with the x86 family, modern set of functional capabilities based on PCI Express / SATA / Gbit Ethernet / USB interfaces, hardware coding / decoding of video, low-energy consumption and ultra-small dimensions, as well as operation in the extended temperature range (-40...+85°C). The used Intel® Atom<sup>™</sup> Queens Bay CPU platform, which contains E6x0T CPU and EG20T controller hub is characterized with high performance, although has a low energy consumption and heat release: E680T (1.6 GHz) TDP = 6 W, E620T (0.6 GHZ) TDP = 4.8 W), as well as announced by manufacturer operation in the extended temperature range (-40...+85°C). The used solution requires neither a bulky heat-sink nor a forced cooling of the fan) while working in the whole operating temperature range, which is especially important when building the onboard control systems.

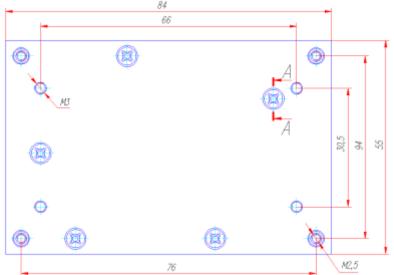

The applied COM Express® mini form-factor has ultra-low dimensions (55 84 mm) and uses a standard COM Express® Type10 connector (fully compatible with COM Express® COM.0 Type 10 connector, the CPU& module fully conformal with the "PICMG® COM.0 COM Express® Module Base Specification Revision 2.1").

CPB907 is mainly used as a compute kernel with a wide range of I/O interfaces when building real-time systems, safety and communication onboard systems, video coding and decoding systems, manufacturing control systems, high-speed data acquisition as well as for other critical applications, designed for operation in harsh environments.

The CPB907 CPU Module is installed on the carrier board, which provides access to the main I/O ports. All primary interface signals are routed to the high-density 220-pin connector (3-6318490-6, COM-Express Connector Socket 220-pin Type 10, TYCO).

For more details on COM Express® standard, please visit PICMG® official website at: <u>http://www.picmg.com/</u>.

# **1.2. General Information**

- **CPU:** Intel® Atom<sup>™</sup> E6x0T

- Frequency: 0.6 GHz (E620T) / 1.6 GHz (E680T)

- IA32 x86 kernel

- 32 bit memory bus

CPB907 Mezzanine CPU Module COM Express Express® mini, Type 10 Fastwel

- Level 1 cache (32 KB)

- Level 2 cache (512 KB)

- Hyper-Threading (2 Threads)

- Intel SpeedStep

- Support of Deep Power Down

- SIMD Extension 2&3 (SSE2, SSE3, SSSE3)

- Companion chip: Intel EG20T controller hub

- RAM:

- Soldered DDR2-800 SDRAM 1 GB

- Integrated graphics coprocessor:

- Frequency: 400 MHz

- 2D/3D acceleration

- Hardware video decoding (H.264, MPEG2, MPEG4, VC1, WMV9)

- Hardware video coding (H.264, MPEG4, H.263) 1

- Independent connection of two displays

- Video memory is allocated from the system memory

- FLASH BIOS:

- 1 MB, modifiable within the system and a backup copy

- Integrated nonvolatile memory:

- 32 KB FRAM (SPI) for user data (only in CPB907-01/02)

- 8 KB FRAM (I2C) to store configuration

- When there is no battery, the CMOS settings are stored in the FRAM (I2C)

- FLASH-drive (only in CPB907-01):

- Connected to SATA interface (SATA1 port)

- 4 GB NAND Flash (SLC)

- Reading / writing speed 100 / 80 MB/s

- Integrated wear control system and ECC

- Connector for MicroSD cards:

- Support of SD cards, SDHC, speed class 6

- Hardware monotor:

- Module and CPU temperature monitoring (-55 ... +125°C)

- Monitoring of principal supply voltages

- External fan control

- Digital accelerometer (only in CPB907-01/02):

- measuring acceleration along 3 axes

- Resolution: 14 / 8 bit

- Programmable measuring range ±2g / ±4g / ±8g/

- Determination of events: free fall, movement, shaking, changing spatial orientation

- Generation of event trapping

- Digital pressure indicator (only in CPB907-01/02):

- Pressure measuring range: 50 ... 115 KPa

- Conversion range: 1 ms

- Resolution: 0.15 KPa

1 only for CPB907-01, CPB907-02 (is stipulated by E620T CPU limitations)

standard measurement accuracy ±1 KPa (at the temperature from -20 to +85°C, calibration testing during manufacturing of a microchip, fractional error is not rated).

#### ■ Signals of COM Express® Type 10 connector:

- 3x ports PCIe x1 (PCIe Spec. Rev 1.0a), 2.5 GB/s;

- 6x ports USB 2.0 (host);

- 1x port USB 2.0 (client);

- 2x ports SATA II (1.5-Gbps Gen. I & 3-Gbps Gen II); 2

- Port "LAN 0": Gbit Ethernet;

- Port SPI (External Boot);

- Port "LVDS Ch. A": 18/24-bit, 1280x768 @ 60Hz;

- Port DDI: SDVO, 1920x1080 @ 50Hz;

- Port LPC (Spec. Rev. 1.1);

- Port SMBus (Spec. Rev. 2.0);

- Port I2C;

- Port HD Audio;

- Port "Speaker Out";

- Port SDIO (compatible with GPIO ports);

- Port RS-232 (CMOS 3.3V, 256-byte FIFO, up to 4xMbps);

- Port RS-232 (CMOS 3.3V, 64-byte FIFO, up to 1xMbps) or CAN 2.0B Active (CMOS 3.3V, up to 1xMbps);

- Port "RTC battery".

- Real -Time Clock 3

- Watchdog timer:

- CPU integrated 1 µs ...10 minutes

- OS compatible:

- Microsoft<sup>™</sup> MS-DOS<sub>®</sub>6.22, FreeDOS

- Linux 2.6

- QNX 6.4x

- Microsoft<sup>™</sup> Windows<sub>®</sub> CE 6.0

- Microsoft<sup>™</sup> Windows<sub>®</sub> XP (Embedded)

- Microsoft<sup>™</sup> Windows<sub>®</sub>7 (Embedded)

- console ports: COM1 / COM2

- Supply voltage:

- +4.75...+20.0 V (primary)

- +5 V ±5% (Standby mode S3) 4

- Short circuit and overvoltage protection.

<sup>2</sup> only SATA0 for CPB907-01 (SATA1 port in version CPB907-01 is occupied by the integrated SATA SSD)

<sup>3.</sup> The battery is not included into the delivery checklist of CPB907, for operation of real-time clock it is required to install the battery or other uninterruptable power supply on the carrier-board.

<sup>4.</sup> Availability of a voltage source for standby mode 5 V (Standby) is not obligatory for module's operation.

- 9.0 W for CPB907-01/-02 (operating mode, 12V @ 0.75A);

- 7.5 W for CPB907-03 (operating mode, 12V @ 0.62A);

- 1 W (standby mode, 5V @ 0.2A).

- Operating temperature range:

- -40°C ... +85°C;

#### Humidity:

- 5% ... 95%, at +25°C without condensation;

- Shock-/ Vibration resistance:

- 50g / 5g

- (MTBF):

- No less than: 200 000 hours 5

- Dimensions:

- No more than: 55.0 × 84.0 × 15.0 mm;

• Overall height, with cooling system (from the bottom surface of module plate to the upper surface heat-distributing plate or heat-sink):

- 13.0 mm (heat-distributing plate is installed, complies with the COM Express v2.1 specification);

- 15.0 mm (finned heatsink is installed);

#### Module weight:

- No more than 45 g.;

- Weight of the module with cooling system:

- No more than 125 g (heat-distributing plate is installed)

- не более 145 г (установлен радиатор с оребрением)

<sup>5.</sup> The value is calculated according to: Telcordia Issue 1 model, Method I Case 3, for continuous operation at a surface location, under normal environmental conditions (Moderately Cold climate 4) and at ambient temperatures 30°C.

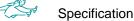

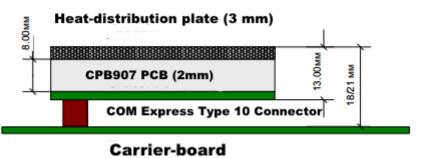

# 1.3. Dimensions

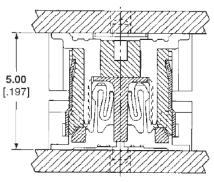

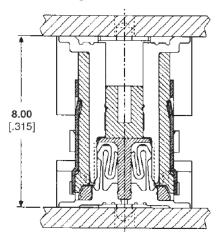

This subsection specifies overall and fitting dimensions of CPB907 and carrier-board. Maximum allowed height of components, installed on the upper side of the carrier-board directly under CPB907, amounts to:

- 5 mm when there is an 8 mm mating COM Express connector (3-6318491-6, TYCO) installed on the carrier-board;

- 2 mm when there is an 8 mm mating COM Express connector (3-1827253-6, TYCO) installed on the carrier-board.

Fig. 1-1: Overall and fitting dimensions of CPB907 (bottom and side view)

This figure shows CPB907 module as viewed from the side of the primary COM-Express Connector Socket 220-pin.

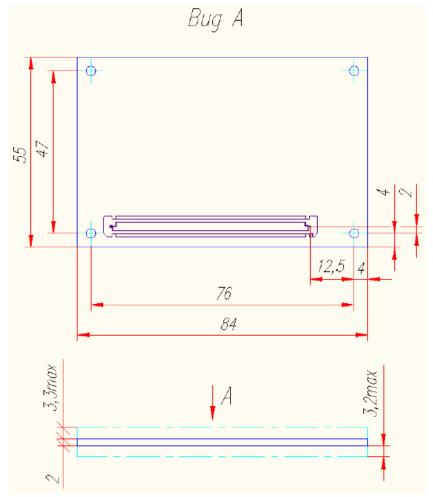

Fig. 1-2: Overall dimensions of the carrier-board's installation spot

This figure with dotted lines shows the location of CPB907 on the carrier-board, as well as overall dimensions of the installation spot.

# 1.4. Module power supply

Module power supply should correspond to the requirements, specified in the table 1-1. Power is supplied to the module via COM Express connector.

The power supply source should ensure starting current and load current, specified in the table below depending on the module version (starting currents and load currents are specified at rated voltage values). When choosing the power supply, it is required to consider starting current of CPB907 and consumption current of mezzanine modules as well as other devices, connected to the ports of CPB907. Input "+12 V" is equipped with short-circuit (7.5 A) and overvoltage protection (up to 25 V).

| Version                | Power supply voltage, V | Voltage limit values, V | Load current, A                             | Starting current |

|------------------------|-------------------------|-------------------------|---------------------------------------------|------------------|

| CPB907-01<br>CPB907-02 | +5 (Standby)            | от +4.75 до +5.25       | 0.15 @ 5 V                                  | 0.5              |

| CPB907-03              | +12                     | от +4.75 до +20         | 2.0 A @ 5 V<br>0.8 A @ 12 V<br>0.5 A @ 20 V | 2.0              |

Table 1-1: Requirements for power supply parameters

\* Consumption current information is preliminary.

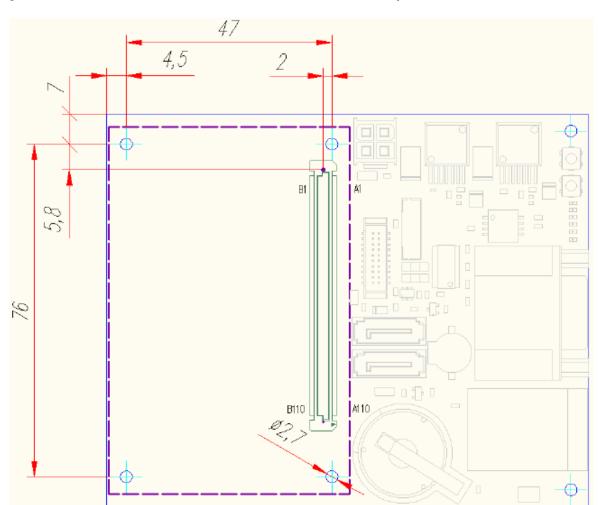

# 1.5. Block diagram of CPB907

#### Fig. 1-3: Block diagram of CPB907

# 1.6. Location of main components of CPB907

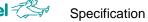

Fig. 1-4: Location of main components of CPB907

Location of the module's components can differ from the one on the figure.

Purposes of module's connectors are described in the Section "Integral parts of CPB907" and in section Tables of module's connector's contacts.

Purposes of X1...X2 switches are specified in the section Installation of module's switches.

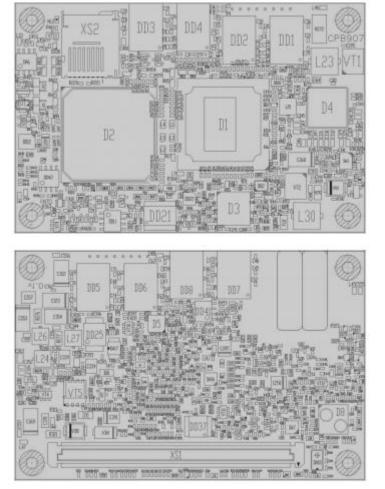

### 1.7. Installation of CPB907 onto the carrier-board, cooling system

The heat-distribution plate (order number code contains "-R1") is mounted on the top side of the board in accordance with the COM Express specification. The maximum height of components on the top side of the CPB907 board is defined by the COM Express standard and amounts to 5 mm.

The CPB907 module comes with a heat-distribution plate or a heat-sink with fins. The maximum overall height of the module with the installed heat-distribution plate (exclusive of COM Express connector) is 13 mm.

Heat is transferred to the heat-distribution plate is transferred from the following microchips: E6x0T CPU, EG20T controller hub, power management integrated circuits (PMIC), DDR2 memory chips mounted on the top side of the CPB907 board.

Additionally, the heat-distribution plate enables to mount a heat-sink on it.

The maximum height of the heat-sink amounts to 8 mm, thermal resistance of the heat-sink is equal to 5 C/W (without forced cooling /fan). The heat-sink is supplied as an optional accessory (ACS30067). When installing the hat-sink from a kit ACS30067 onto the heat-distribution plate, the total overall height of the module (exclusive of COM Express Connector) will be 21 mm. It is also possible to include a heat-sink with ribs into the delivery package instead of the heat-distribution plate (order number code contains "-R2"), ensuring the module operation in the entire temperature range without setting an additional heat-sink and heat transfer to the enclosure. When using the

"-R2" ribbed heat-sink, a total overall height of the module (exclusive of COM Express Connector) is 15 mm.

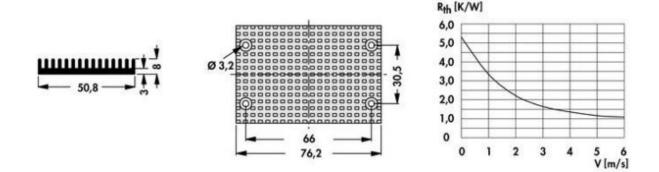

#### Fig. 1-6: Dimensions of the heat-dissipation plate

Fig. 1-7: Overall Dimensions of heat-sink (ACS30067) and dependency of its heat-transfer on the generated power and air-flow rate

### 1.8. Versions

CPB907 CPU module has six major versions.

**SPB907-01-E1.6-RAM1024-SSD4G-R1-I** - CPB907 CPU Module (COM Express® mini, Type10), Intel E680T 1.6 GHz, 1 GB DDR2 SDRAM, 4GB SSD, slot MicroSD, FRAM 32 KB, accelerometer, pressure sensor, heat-distribution plate.

**SPB907-01-E1.6-RAM1024-SSD4G-R2-I** - CPB907 CPU Module (COM Express® mini, Type10), Intel E680T 1.6 GHz, 1 GB DDR2 SDRAM, 4GB SSD, slot MicroSD, FRAM 32 KB, accelerometer, pressure sensor, heat-sink with fins.

**SPB907-02-E1.6-RAM1024-R1-I** - CPB907 CPU Module (COM Express® mini, Type10), Intel E680T 1.6 GHz, 1 GB DDR2 SDRAM, a slot MicroSD, FRAM 32K, accelerometer, pressure sensor, the heat-distribution plate.

**SPB907-02-E1.6-RAM1024-R2-I** - CPB907 CPU Module (COM Express® mini, Type10), Intel E680T 1.6 GHz, 1 GB DDR2 SDRAM, a slot MicroSD, FRAM 32K, accelerometer, pressure sensor, heat-sink with fins.

**SPB907-03-E0.6-RAM1024-R1-I** - CPB907 CPU Module (COM Express® mini, Type10), Intel E620T 600 MHz, 1 GB DDR2 SDRAM, a slot MicroSD, heat-distribution plate.

**SPB907-03-E0.6-RAM1024-R2-I** - CPB907 CPU Module (COM Express® mini, Type10), Intel E620T 600 MHz, 1 GB DDR2 SDRAM, a slot MicroSD, heat-sink with fins.

Differences of versions are summarized in the table below:

| Order<br>number                               | CPU               | Non-<br>volatile<br>memory | Integrated<br>SSD | SATA<br>ports                 | Sensors                                       | Cooling<br>system in<br>kit    |

|-----------------------------------------------|-------------------|----------------------------|-------------------|-------------------------------|-----------------------------------------------|--------------------------------|

| CPB907-01-<br>E1.6-<br>RAM1024-<br>SSD4G-R1-I | E680T, 1.6<br>GHz | FRAM 32<br>KB              | 4GB               | 1 x port<br>(COM<br>Express)  | Acceleration<br>and<br>temperature<br>sensors | Heat-<br>distribution<br>plate |

| CPB907-01-<br>E1.6-<br>RAM1024-<br>SSD4G-R2-I |                   |                            |                   |                               |                                               | Heat-sink<br>with fins         |

| CPB907-02-<br>E1.6-<br>RAM1024-<br>R1-I       |                   |                            | -                 | 2 x ports<br>(COM<br>Express) |                                               | Heat-<br>distribution<br>plate |

| CPB907-02-<br>E1.6-<br>RAM1024-<br>R2-I       |                   |                            |                   |                               |                                               | Heat-sink<br>with fins         |

| CPB907-03-<br>E0.6-<br>RAM1024-<br>R1-I       | E620T, 0.6<br>GHz | -                          |                   |                               | Temperature sensors                           | Heat-<br>distribution<br>plate |

| CPB907-03-<br>E0.6-<br>RAM1024-<br>R2-I       |                   |                            |                   |                               |                                               | Heat-sink<br>with fins         |

| Table 1-2: Options of CPB907 Module (differences of the supplied versions) |

|----------------------------------------------------------------------------|

|----------------------------------------------------------------------------|

#### **Options available:**

| \WCE6 | Windows CE 6.0      |

|-------|---------------------|

| \LNX  | Linux 2.6           |

| \WXPE | Windows XP Embedded |

| COATING |                   |

|---------|-------------------|

| \COATED | Conformal coating |

\* Information on the availability of pre-installed QNX operating system is provided upon individual request.

\*\* If the module is ordered without any kits, it is required to specify "\OEM" option at the time of order.

### **1.9. Delivery checklist**

Standard delivery checklist of CPB907 CPU Module includes:

- 1. CPB907 Module;

- 2. Heat-distribution plate / Heat-sink with fins;

- 3. Assembly kit for installation of COM Express mini modules onto the carrier-board (5 and 8 mm);

- 4. Package.

# 1.10. Additional accessories

Table 1-3: Additional accessories for CPB907 CPU Module

| KIB1283-02 | Developer's kit for COM Express mini modules                                        |

|------------|-------------------------------------------------------------------------------------|

| ACS30067   | Heat-sink for COM Express mini modules (installed onto the heat-distribution plate) |

# 1.11. Component parts of CPB907

#### 1.11.1. Main high-density COM Express connector (XS1)

All primary interfaces are routed to 220-pin high-density connector (3-6318490-6, COM Express Connector Socket 220-pin Type I, TYCO). Below is the view from the back of the CPB907 board, overlooking the COM Express connector.

# Fig. 1-8: Main 220-pin high-density connector of CPB907 module (viewed from the bottom of CPB907).

As a counterpart of the COM Express connector, it is recommended to use on the carrier-board:

- 3-1827253-6 (TYCO) distance between the CPB907 board and the carrier-board: 5 mm

- 3-6318491-6 (TYCO) distance between the CPB907 board and the carrier-board: 8 mm.

# Fig. 1-9: Connection of the COM-Express CPB907 and counterpart of the carrier-board5mm Height8mm Height

(Signal Position)

(Signal Position)

#### 1.11.2. E620T / E680T CPU

CPB907 is built on the basis of x86-compatible 32-bit Intel® Atom™ E620T / E680T CPU (depending on CPB907 version), manufactured on the basis of 45 Nm technology, with low power consumption and industrial operating temperature range (-40 ... +85°C). Operating clock frequency – 600 MHz (E620T) /1.6 GHz (E680T). For more information please visit manufacturer's website at: http://ark.intel.com/ru/products/series/52490.

It represents a highly-integrated solution, combining Intel® Atom™ core, 32-bit DDR2 SDRAM memory controller (up to 2 GB, 400 MHz), graphics subsystem with 2D/3D acceleration (video processor frequency: 400 MHz), extension buses 4 PCIe x1 (1.0a) and LPC (1.1), High Definition Audio subsystem, SMBus, SPI, up to 14 GPIO lines, Real Time Clock. The CPU has implemented a hardware support of video coding (MPEG-4 / H.263 / H.264 - only in E680T), as well as hardware acceleration of video decoding (H.264 / MPEG2 / MPEG4 / VC1 / WMV9 - in E620T and E680T).

#### 1.11.3. EG20T Controller Hub

The module uses Intel® EG20T (Topcliff) controller hub, manufactured in accordance with 90 Nm technology, with low power consumption and industrial temperature range (-40 ... +85°C). For exchanging data with CPU PCIe x1 bus will be used. EG20T represents a highly-integrated controller of such interfaces as: 6 x USB 2.0 (host), USB 2.0 (device), Gbit Ethernet (MAC), 2 x SATA II, 2 x SDIO, SPI, I2C, 4 x UART, CAN.

#### 1.11.4. Random Access Memory (RAM)

As system memory, the CPB907 module uses 1GB DDR2 SDRAM operating at a frequency of 400 MHz.

Installation of memory extension module is not provided.

#### 1.11.5. FLASH BIOS Read-Only Memory

In order to store the Basic I/O system (hereinafter referred to as the BIOS), the module uses 2MB SPI-FLASH (SST25VF016B).

Loading from and external SPI-FLASH microchip installed onto the carrier board, is supported too.

#### 1.11.6. Non-Volatile Memory

For storing user data in the module, FRAM 32 KB (Ramtron, FM25L256) non-volatile memory is provided, and is will be used as a replacement for a standard non-volatile random access memory. For exchanging data with SPI FRAM 32 KB, SPI interface of EG20T chipset will be used. Manufacturer guarantees 100 trillion read/write cycles, which, within such application mode, will be equivalent to ~ 340 years of application (in case of continuous cyclic write-read procedure).

For storing this configuration, a separate 8 KB FRAM non-volatile memory will be used, which is connected to the CPU SMBus interface. If there is no battery, CMOS settings will be stored in FRAM. This memory could be additionally used for storing calibration factors of acceleration sensor.

A separate 512 Kb 25LC512-I/SN microchip of EEPROM memory will be used for storing MACaddress of Gbit Ethernet controller integrated into EG20T chipset.

#### 1.11.7 RTC, CMOS

Real-time clock is integrated into CPU. In case of the switched off power supply, clock operability is ensured via "RTC battery" port of COM-Express connector, from the carrier-board. Battery current consumption amounts to 12  $\mu$ A (standard value), which corresponds to 2 years of use from a standard CR2032 lithium-battery of 220 mAh, provided that the module has been in off state for 24 hours (battery should be installed into the carrier-board). However, an actual battery service life relies heavily on ambient temperature, as well as on the fact, how long time system has been off.

It is recommended to change the battery each 2 years of operation, not awaiting its end of life.

When changing battery, observe the polarity ("+" should be on top). The used battery should be disposed in accordance with the established regulations.

BIOS settings are stored in a separate non-volatile memory FRAM (8 KB).

#### 1.11.8. Slot for MicroSD cards

The module enables the use of MicroSD Card as drive (SDSC, SDHC, Spec. v1.1, v2.0), for this purpose, the top side of the board has a relevant MicroSD (XS2) connector. "Push-Push" socket (DM3B-DSF-PEJ, Hirose) is used. This type of connector allows for a horizontal card removal. The connector located in such a way that availability of a heat-distribution plate or heat-sink would not prevent removal of the MicroSD card.

#### 1.11.9. Integrated SATA SSD

As an option (only in the delivered configuration CPB907-01), the module is equipped with 4GB SATA SSD (port SATA1 of EG20T controller hub). Controller and 2 microchips SLC NAND Flash are integrated in a single chip.

Read / write speed is 100 / 80 MB/s, there is an integrated wear control system and hardware error correction mechanism ECC (8/15 bit to 512 byte, 16/30 bit to 1 KB). MTBF of the drive amounts to 2 000 000 hours.

#### 1.11.10. PCI Express port (XS1)

3x ports PCIe x1 are routed to the COM Express connector. Specification PCIe Spec. Rev 1.0a is supported, data exchange speed – up to 2.5 GB/s.

#### 1.11.11. SATA port (XS1)

2x SATA ports (in the delivered configuration CPB907-01 there is only 1x SATA port (SATA0) available, since SATA0 port in CPB907-01 is used for the connection of integrated 4 GB SSD), are routed to the COM Express connector. Support of SATA I, SATA II specifications. SATA0/SATA1 ports of EG20T controller hub are used.

#### 1.11.12. USB 2.0 port (XS1)

The module has 6 x USB Host ports, as well as 1x USB Device port with support of USB 1.1 and USB 2.0 specifications. The USB ports are routed to the COM Express connector.

#### 1.11.13. Gbit Ethernet port (XS1)

The module has 1x Gbit Ethernet port. Gigabit Ethernet MAC controller integrated into the controller hub is used. 88E1510-A0-NNB2I000 (Marvell) is used as PHY. Port is routed to the COM Express connector. Support of the following operation modes: 10/100/1000 Mb.

#### 1.11.14. COM1 / COM2 (XS1) serial ports

The CPU module has two asynchronous serial ports: COM1 and COM2. COM1 – 2-wire interface UART (CMOS, 3.3V), speed up to 4Mb/s, FIFO buffer 256 byte (EG20T, UART0). COM2 – 2-wire interface UART (CMOS, 3.3V), speed up to 1Mb/s, FIFO buffer 64 byte (EG20T, UART1) or CAN 2.0B (CMOS, 3.3V), speed up to 1Mb/s (EG20T, CAN-port). Configuration of the port (UART or CAN) is selected by software, using BIOS Setup settings, by default - UART.

The both ports are routed to the COM Express connector and can be used for console input/output and loading files (COM1 port will be used as a console port, by default). Overvoltage protection up to 14 V (which is associated with COM-Express Type 1 and Type 10 compatibility requirements) is implemented.

The UART ports are fully software-compatible with the UART 16550 version.

CAN port is compatible with "BOSCH CAN Protocol Version 2.0B Active" (standard and extended format) in accordance with ISO 11519, ISO 11898, and SAEJ2411.

In order to enable the ports to operate within networks RS-232, RS-422/485 or CAN it is required to equip the carrier-board with relevant transmitter-/receiver units.

Data exchange speed over serial ports can be set in the BIOS Setup settings. The data exchange speed is determined by the value of CPU frequency divider register. The divider's value will be calculated according to the following formula:

# DIV = F / BR, BR=F / (DIV×16)

### where

F – is an internal generator's frequency [MHz];

$\mathsf{F}$  = (12.288, 25, 48) ×PLL2VCO×BAUDDIV ( PLL2VCO = 1…6, BAUDDIV = 1…16 ) maximum value  $\mathsf{F}$  = 192 MHz

- DIV divider's value (minimum value DIV = 1);

- BR exchange rate required [bit/s].

The receiver tolerates deviations of data exchange rate by 3,0% downward and by 2,5% - upward.

The below table has values frequency divider for a number of data exchange rates:

|                          | 1         |                                          |          |                                         |          |                                        |

|--------------------------|-----------|------------------------------------------|----------|-----------------------------------------|----------|----------------------------------------|

| Exchange<br>rate, bit/s. | F=175 MHz | (CLK=25 MHz<br>MPLL2VCO=7,<br>BAUDDIV=1) | F=25 MHz | (CLK=25 MHz<br>PLL2VCO=1,<br>BAUDDIV=1) | F=48 MHz | (CLK=25MHz<br>PLL2VCO=1,<br>BAUDDIV=1) |

|                          | Divider   | Error, %                                 | Divider  | Error, %                                | Divider  | Error, %                               |

| 300                      | 36458     | - 0.001                                  | 5208     | - 0.006                                 | 10000    | 0.000                                  |

| 600                      | 18229     | - 0.001                                  | 2604     | - 0.006                                 | 5000     | 0.000                                  |

| 1200                     | 9115      | + 0.005                                  | 1302     | - 0.006                                 | 2500     | 0.000                                  |

| 2400                     | 4557      | - 0.006                                  | 651      | - 0.006                                 | 1250     | 0.000                                  |

| 4800                     | 2279      | + 0.016                                  | 326      | + 0.147                                 | 625      | 0.000                                  |

| 7200                     | 1519      | - 0.006                                  | 217      | - 0.006                                 | 417      | + 0.080                                |

| 9600                     | 1139      | - 0.028                                  | 163      | + 0.147                                 | 313      | + 0.160                                |

| 14400                    | 760       | + 0.059                                  | 109      | + 0.452                                 | 208      | - 0.160                                |

| 19200                    | 570       | + 0.059                                  | 81       | - 0.469                                 | 156      | - 0.160                                |

| 28800                    | 380       | + 0.059                                  | 54       | - 0.469                                 | 104      | - 0.160                                |

| 38400                    | 285       | + 0.059                                  | 41       | + 0.756                                 | 78       | - 0.160                                |

| 57600                    | 190       | + 0.059                                  | 27       | - 0.469                                 | 52       | - 0.160                                |

| 115200                   | 95        | + 0.059                                  | -        | -                                       | 26       | - 0.160                                |

| 230400                   | 47        | - 1.004                                  | -        | -                                       | 13       | - 0.160                                |

| 256000                   | 43        | + 0.640                                  | 6        | - 1.725                                 | 12       | + 2.343                                |

| 312500                   | 35        | + 0,000                                  | 5        | 0.000                                   | -        | -                                      |

| 460800                   | 24        | + 1,100                                  | -        | -                                       | -        | -                                      |

| 921600                   | 12        | + 1,100                                  | -        | -                                       | -        | -                                      |

| 1843200                  | 6         | + 1,100                                  | -        | -                                       | -        | -                                      |

| 1000000                  | 11        | + 0,568                                  | -        | -                                       | 3        | 0.000                                  |

| 1500000                  | -         | -                                        | -        | -                                       | 2        | 0.000                                  |

| 3000000                  | -         | -                                        | -        | -                                       | 1        | 0.000                                  |

Table 1-4: Values of frequency dividers for serial ports

### 1.11.15. LVDS and SDVO ports (XS1)

For connection of LCD(TFT)-panels, LVDS interface is used. This interface is routed to the COM Express connector. Color depth may amount to 24 bits (18-bit mode is also supported). Maximum resolution: 1280 x 768 @ 60Hz. LVDS interface may be routed directly to the LVDS connector on carrier-board.

SDVO interface is also routed to the COM Express connector. Maximum resolution: 1920 x 1080 @ 50Hz. For connection of the video units, the carrier-board should be equipped with a relevant converter: SDVO – CRT (e.g. CH7317B Chrontel), SDVO – DVI, SDVO – HDMI, SDVO – LVDS (e.g. CH7308B Chrontel).

Independent operation of two displays is supported.

For operation of LVDS-panel or other video output devices in Linux, WindowsXP, Windows7 operating systems, it is required to use Intel IEMGD suite, which latest version can be downloaded from the official website at: <u>http://www.intel.ru</u>.

#### 1.11.16. HDA port (XS1)

For connection of audio devices, High Definition Audio interface (controller is integrated into the EG20T controller hub) is routed to the COM Express connector.

Operation of the audio port requires the carrier board to have a relevant audio codec (e.g. CS4207 Cirrus Logic) installed.

#### 1.11.17. SDIO / GPIO port (XS1)

GPIO port of the controller hub (EG20T) is used. The port is intended for input/output of 8 logic signals. Interrupt generation becomes possible over each of the GPIO lines.

The port is software-compatible with SDIO port, on COM Express connector (CMOS level, 5V Tolerant).

Port configuration is software-selectable, in BIOS Setup settings (GPIO port, by default).

#### 1.11.18. Acceleration, pressure and temperature sensors, hardware monitor

A capacitive micromachined accelerometer MMA8451Q (Freescale) is used as acceleration sensor<sup>6</sup>. This device, having 8/14 bit resolution, enables to measure acceleration along three axes, вибраций в диапазонах 2/4/8 g, determine slope angle, free fall, detect pulse and jolts. Relative measurement errors are not rated.

The module is also equipped with a Miniature I2C Digital Barometer <sup>7</sup> MPL115A2 (Freescale), which provides accurate pressure measurements from 50 to 115 kPa (standard measuring precision is 1 kPa, with the operating temperature range that spans from -20 to +85°C, resolution of 0.15 KPa). Calibration of the device is carried out by the manufacturer during production process. Relative measurement errors are not rated.

The acceleration and pressure sensors are connected to SMBus of the CPU and enable generating system interrupts for events. The measurement errors are not rated, the standard measurement errors are defined by characteristics, stated by device manufacturers.

The used LM87 and LM96163 hardware monitors enable to control module's main voltages, module's and CPU temperature, as well as to control an external fan.

6 only in CPB907-01, CPB907-02 7 only in CPB907-01, CPB907-02

#### 1.11.19. Watchdog timer

The module uses 1 hardware watchdog timer, integrated into the processor chip, with the modifiable actuation range from 1  $\mu$ s to 10 minutes.

A logic signal of watchdog timer actuation (CMOS, 3.3В - при срабатывании сторожевого таймера состояние линии переходит в логическую единицу) is routed to the COM Express connector.

#### 1.11.20. Reset and power supply monitoring

Module reset signal is generated from the following sources:

From supervisor at the time of power up;

From the external reset signal from the COM Express connector;

From the watchdog timer.

CPU switch from the standby mode (from S3 state to S0 state) can be carried out from the following sources, from COM Express connector:

Gbit Ethernet 0 port (Magic Packet);

COM1 port;

GPIO port;

USB port;

WAKE# signal.

#### 1.11.21. LPC port (XS1)

LPC port includes all signals of LPC extension bus, except for DRQ signal and is routed to the COM Express connector (direct access mode is not supported by LPC bus controller). Support of LPC Rev 1.1. specification.

#### 1.11.22. SMBus and I2C ports (XS1)

SMBus CPU port is routed to the relevant port of COM Express connector. Additionally, lines of I2C interface of EG20T controller hub are routed to the COM Express connector.

#### 1.11.23. PC-buzzer port (XS1)

PC-buzzer port is routed to the COM Express connector.

#### 1.11.24. LEDs

#### Table 1-5: Purpose of CPB907 LEDs

| LED | Function                                      |

|-----|-----------------------------------------------|

| HL1 | Diagnostic input power supply LED (green)     |

| HL2 | LED of module's MicroSD card activity (green) |

| HL3 | LED of integrated SATA SSD activity (green)   |

During module's normal operation, after power-up, the HL1 LED is lighted with green. HL1 is off when there is a short circuit or there is no input power supply voltage of "12 V". The HL2-HL3 LEDs are flashing when addressing to the relevant devices.

# **SECTION 2**

# **TECHNICAL CHARACTERISTICS**

# 2. Technical specification

#### Table 2-1: Requirements for electric power supply of CPB907 **Electric supply requirements** Power supply voltage "+ 12V" (principal voltage) +12 V (+4.75 ... +20 V) Power supply voltage "+5 V" STANDBY (standby +5 V (+4.75 ... +5.25 V)<sup>8</sup> mode) Consumption current over power supply voltage, no more than: CPB907-01, CPB907-02 1800 mA @ +5V (9.0 W) 750 mA @ +12V (9.0 W) 450 mA @ +20V (9.0 W) 200 mA @ +5V STANDBY (1 W) CPB907-03 1500 mA @ +5V (7.5 W) 625 mA @ +12V (7.5 W) 375 mA @ +20 B (7.5 W) 200 mA @ +5 B STANDBY (1 W) Maximum available current consumed over external circuits (standard value at +25C, limited by the installed resettable fuse): SPI POWER (XS1) 100 mA

#### Table 2-2: Characteristics of GPIO

| Digital I/O                                        |                        |  |

|----------------------------------------------------|------------------------|--|

| Output voltage, Logical 1                          | max. 3.3 V             |  |

| Input voltage, Logical 0                           | max. 0.8 V             |  |

| Input voltage, logical 1                           | min. 2.0 V, max. 5.5 V |  |

| Output voltage, Logical 0 (at the current of 8 mA) | max. 0.4 V             |  |

| Output voltage, Logical 1 (at the current of 8 mA) | min. 2.4 V             |  |

#### Table 2-3: Characteristics of serial ports

| Serial ports                                         |        |  |

|------------------------------------------------------|--------|--|

| Maximum exchange rate via COM1 serial port           | 4 Mb/s |  |

| (UART)                                               |        |  |

| Maximum exchange rate via COM2 serial port<br>(UART) | 1 Mb/s |  |

| Maximum exchange rate via COM2 serial port (CAN)     | 1 Mb/s |  |

#### <sup>8</sup> Additional power supply voltage +5 B STANDBY is not necessary for module's operation

Specification

| SATA port                                              |                                                                                                                                                                                                                 |  |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Number of external SATA devices                        | Up to two devices                                                                                                                                                                                               |  |

|                                                        | SATA0, SATA1 ports                                                                                                                                                                                              |  |

| Supported operation modes of SATA devices              | SATA Gen.1 (1.5 Gb/s), SATA Gen.2 (3.0 Gb/s),                                                                                                                                                                   |  |

| Volume of the integrated SSD (SATA1 port) <sup>9</sup> | 4 GB (NAND Flash, SLC) with the integrated wear<br>control system and hardware error correction<br>mechanism ECC (8/15 bit to 512 byte, 16/30 bit to<br>1 KB).<br>MTBF of the drive amounts to 2 000 000 hours. |  |

#### Table 2-5: Characteristics of USB, Ethernet ports

| USB, Ethernet ports                         |                                                                                    |  |

|---------------------------------------------|------------------------------------------------------------------------------------|--|

| Type of USB ports                           | USB Host, 6x ports                                                                 |  |

|                                             | USB Device, 1x port                                                                |  |

| Types of supported USB-devices              | 1.1, 2.0                                                                           |  |

| Exchange rate over Ethernet channel         | 10/100/1000 Mb/s                                                                   |  |

| LED indication of Ethernet-channel activity | LEDs on the carrier-board: Activity (ACTIVE) and communications link state (LINK). |  |

#### Table 2-6: Mechanical characteristics

| Mechanical characteristics                        |                                                  |  |

|---------------------------------------------------|--------------------------------------------------|--|

| Vibration resistance                              | 5 g (acceleration amplitude)                     |  |

| Single shock resistance                           | 100 g (peak acceleration)                        |  |

| Multiple shocks resistance                        | 50 g (peak acceleration)                         |  |

| Overall dimensions of module, no more than        | 55 84 15 mm                                      |  |

| Overall height of the module with cooling system, | 13 mm (corresponding to the COM Express          |  |

| exclusive of COM Express connector                | specification)                                   |  |

| Module weight, no more than                       | 45 g (without MicroSD card and heat distribution |  |

|                                                   | plate)                                           |  |

| Module weight with cooling system, no more than   | 125 g (heat distribution plate is installed)     |  |

|                                                   | 145 g (finned heat-sink is installed)            |  |

| MTBF <sup>10</sup>                                | No less than 200 000 hours                       |  |

9 Only for the version CPB907-01.

<sup>10</sup> MTBF values are calculated according to the Telcordia Issue 1 model, Method I Case 3, for continuous operation, located on the ground, at normal environmental conditions (Moderately Cold Climate 4, in accordance with the GOST standard 15150-69) and at ambient temperature 30°C.

18

#### Table 2-7: Environmental conditions

| Environmental conditions            |                                           |  |

|-------------------------------------|-------------------------------------------|--|

| Operating temperature range -40+85C |                                           |  |

| Module storage conditions           | 1 according to the GOST 15150-69 standard |  |

| Relative humidity                   | Up to 80 %, without moisture condensation |  |

| #     | Source by default              | Alternative sources  |

|-------|--------------------------------|----------------------|

| NMI   | -                              | Watchdog Timer (WDT) |

| IRQ0  | Reserved (System Time Clock)   | -                    |

| IRQ1  | PS/2 Keyboard                  | -                    |

| IRQ2  | Reserved (coding)              | -                    |

| IRQ3  | COM2                           | -                    |

| IRQ4  | COM1                           | -                    |

| IRQ5  | External devices               | -                    |

| IRQ6  | USB                            |                      |

| IRQ7  | External devices               | -                    |

| IRQ8  | RTC                            | -                    |

| IRQ9  | External devices               | -                    |

| IRQ10 | External devices               | -                    |

| IRQ11 | External devices               | -                    |

| IRQ12 | PS/2 Mouse                     | -                    |

| IRQ13 | Reserved (Coprocessor support) | -                    |

| IRQ14 | -                              | -                    |

| IRQ15 | -                              | -                    |

Table 2-8: Addresses of hardware interrupts

# 2.3. Module's DMA channels

#### Table 2-9: Module's DMA channels

| #    |                  |

|------|------------------|

| DRQ0 | -                |

| DRQ1 | External devices |

| DRQ2 | External devices |

| DRQ3 | External devices |

| DRQ5 | External devices |

| DRQ6 | External devices |

| DRQ7 | External devices |

# 2.4. Address I/O space

| Address                                 | Function                       | Notes |

|-----------------------------------------|--------------------------------|-------|

| 0000h - 000Fh                           | Slave DMA                      |       |

| 0020h - 0021h                           | Master Interrupt Controller    |       |

| 0022h – 0023h                           | Indirect Access                |       |

| 0040h – 0043h                           | Timer / Counter                |       |

| 0048h - 004Bh                           | PWM Control                    |       |

| 0060h<br>0064h                          | Keyboard / Mouse Control       |       |

| 0061h                                   | NMI Status / Control           |       |

| 0065h<br>0067h                          | WDT Reload                     |       |

| 0068h - 006Dh                           | WDT Control                    |       |

| 0070h – 0071h                           | CMOS Memory / RTC              |       |

| 0072h – 0075h                           | MTBF                           |       |

| 0081h - 008BFh                          | DMA Page                       |       |

| 0092h                                   | System Control                 |       |

| 00A0h - 00A1h                           | Slave Interrupt Controller     |       |

| 00C0h - 00DFh                           | Master DMA                     |       |

| 0278h – 027Fh                           |                                |       |

| 0280h – 02BFh                           |                                |       |

| 02E8h – 02EFh                           |                                |       |

| 02F8h – 02FFh                           | COM2                           |       |

| 03E8h – 03EFh                           |                                |       |

| 03F8h – 03FFh                           | COM1                           |       |

| 0481h – 0483h<br>0487h<br>0489h – 048Bh | DMA High Page                  |       |

| 0490h – 0499h                           | Interrupt Edge / Level Control |       |

| 04D0h - 04D1h                           | Instruction Counter            |       |

| 0CF8h – 0CFFh                           | PCI Configuration              |       |

Table 2-10: Allocation of address I/O space

# 2.5. Address memory space

| Table 2-11. Memory device address |             |                              |  |

|-----------------------------------|-------------|------------------------------|--|

| Address                           | Device      | Notes                        |  |

| 00000 – 9FFFFh                    | DOS         | DOS Area 640 Kbyte           |  |

| A0000 – BFFFFh                    |             | Область видеопамяти 128      |  |

|                                   |             | Kbyte                        |  |

| C0000 – CFFFFh                    |             |                              |  |

| D0000 – DFFFFh                    |             |                              |  |

| E0000 – EFFFFh                    | System BIOS | Extended System BIOS area 64 |  |

|                                   |             | KB (16 KB x 4)               |  |

| F0000 – FFFFFh                    | System BIOS | System BIOS area 64 KB       |  |

#### Table 2-11: Memory device address